为了提高肖特基二极管的雪崩耐量,以避免元器件的雪崩损坏,三安集成电路在18年10月29日申请了一项名为“新型碳化硅结势垒肖特基二极管及其制作方法”的发明专利(申请号:201811267285.X),申请人为厦门市三安集成电路有限公司。

根据目前该专利公开的资料,让我们一起来看看这项肖特基二极管专利吧。

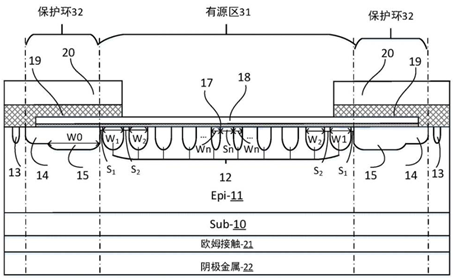

如上图为新型碳化硅结势垒肖特基二极管的分层结构图,该结构中包括层叠设置的第一导电类型碳化硅衬底10和第一导电类型碳化硅外延层11。第一导电类型碳化硅外延层的上表面由中心向外依次设置有有源区31、保护环32和第二导电类型终端场限环13,有源区包括间隔设置的多个第二导电类型结势垒区12。

沿着保护环向有源区的中心的方向,相邻第二导电类型结势垒区的间距逐渐增大,且第二导电类型结势垒区的宽度逐渐减小。有源区包括n个第二导电类型结势垒区,靠近保护环的第一个结势垒区的宽度W1为1-15um;保护环32与第一个结势垒区的间距S1为0.5-8um;第n个第二导电类型结势垒区的宽度Wn为0 .5-4um,第n-1个第二导电类型结势垒区与第n个第二导电类型结势垒区的间距Sn为5-10um。

这样的结构,主要是因为结势垒区之间的间隔逐渐增大后,当施加的反向偏压不断增加,有源区靠近中心处结势垒区之间的间距较大,肖特基结的电场强度较大,由于肖特基效应,导致该区域的肖特基势垒高度降低,成为击穿薄弱点,因此将击穿点引入到有源区中心区域,增加了雪崩状态下的散热面积,从而提高了雪崩耐量!

如上图所示,每一个第二导电类型结势垒12区包括一个子结势垒区,并且第二导电类型结势垒区为长条形,沿着保护环的两侧向有源区31的中心的方向,相邻第二导电类型结势垒区的间距逐渐增大,且第二导电类型结势垒区的宽度逐渐减小。

下面我们再来聊聊这种新型碳化硅结势垒肖特基二极管的制作方法,如下图所示。

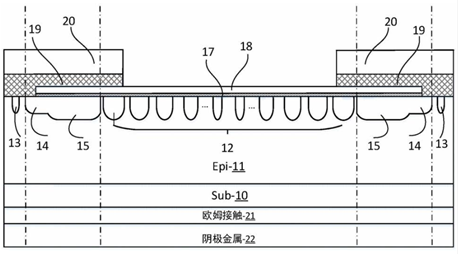

首先,准备碳化硅衬底10,其电阻率为0.001-0.05Ω·cm,厚度200-380um。在碳化硅衬底上,生长第一导电类型的碳化硅外延层11,在碳化硅外延层上表面,通过淀积SiO2、光刻、选择性离子注入形成间隔设置的多个第二导电类型结势垒区12和深结15,深结位于第二导电类型结势垒区外,并且深结和第二导电类型结势垒区的深度相同。

多个第二导电类型结势垒区沿着由外向内的方向,相邻第二导电类型结势垒区的间距逐渐增大,且第二导电类型结势垒区12的宽度逐渐减小。在碳化硅外延层上表面,通过光刻、选择性离子注入形成深度相同的第二导电类型终端场限环13和浅结14。

接着,通过物理研磨,将碳化硅衬底的背面减薄至200-220um,在碳化硅衬底的背面通过电子束蒸发淀积金属Ni,并在900℃下退火形成欧姆接触21,在碳化硅外延层上表面,通过电子束蒸发或溅镀,淀积金属Ti,并在500℃下退火形成肖特基金属17。

最后,在肖特基金属的上表面,通过电子束蒸发淀积金属Al,形成阳极18,在碳化硅外延层上表面及阳极金属的上表面,通过PECVD,淀积形成SiO2/Si3N4层,通过光刻、形成钝化层19,在钝化层的上表面,通过淀积、光刻形成保护层20,在欧姆接触21的下表面,通过淀积,形成TiNiAg阴极金属22。

以上就是三安集成电路的新型碳化硅结势垒肖特基二极管发明专利,二极管是电子产品的主要部件之一,优质的二极管是保证电子产品稳定性的源头,而三安集成电路这项专利正好填补了这方面的空缺,从而使得电子产品的质量大大提高!